# Technical Description for Thor-8-PCIe

Doc. No. 1111-1-HAA-1097-1

Rev. 1.0

November 7, 2012

#### Copyright

Copyright (C) Odin TeleSystems Inc., 2011-2012. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of Odin TeleSystems Inc., 800 East Campbell Road, Suite 334, Richardson, Texas 75081, U. S. A.

#### **Trademarks**

Odin TeleSystems, the Odin Logo, OTX, and Thor-8-PCIe are trademarks of Odin TeleSystems Inc., which may be registered in some jurisdictions. Other trademarks are the property of their respective companies.

#### Changes

The material in this document is for information only and is subject to change without notice. While reasonable efforts have been made in the preparation of this document to assure its accuracy, Odin TeleSystems Inc., assumes no liability resulting from errors or omissions in this document, or from the use of the information contained herein.

Odin TeleSystems Inc. reserves the right to make changes in the product design without reservation and notification to its users.

#### Warranties

THE PRODUCT AND ITS DOCUMENTATION ARE PROVIDED "AS IS" AND WITHOUT WARRANTY OF ANY KIND. ODIN TELESYSTEMS EXPRESSLY DISCLAIMS ALL THE WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANT-ABILITY AND FITNESS FOR PARTICULAR PURPOSE. ODIN TELESYSTEMS DOES NOT WARRANT THAT THE FUNCTIONALITY OF THE PRODUCT WILL MEET ANY REQUIREMENTS, OR THAT THE OPERATIONS OF THE PRODUCT WILL BE UNINTERRUPTED OR ERROR-FREE, OR THAT DEFECTS WILL BE CORRECTED. FURTHERMORE, ODIN TELESYSTEMS DOES NOT WARRANT OR MAKE ANY REPRESENTATIONS REGARDING THE USE OF THE PRODUCT OR ITS DOCUMENTATION IN TERMS OF THEIR CORRECTNESS, ACCURACY, RELIABILITY, OR OTHERWISE. NO ORAL OR WRITTEN INFORMATION OR ADVISE GIVEN BY ODIN TELESYSTEMS OR ODIN TELESYSTEMS' AUTHORIZED REPRESENTATIVE SHALL CREATE A WARRANTY. SOME JURISDICTIONS DO NOT ALLOW THE EXCLUSION OF IMPLIED WARRANTIES, SO THE ABOVE EXCLUSION MAY NOT APPLY.

UNDER NO CIRCUMSTANCE SHALL ODIN TELESYSTEMS INC., ITS OFFICERS, EMPLOYEES, OR AGENTS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, OR CONSEQUENTIAL DAMAGES (INCLUDING DAMAGES FOR LOSS OF BUSINESS, PROFITS, BUSINESS INTERRUPTION, LOSS OF BUSINESS INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THE PRODUCT AND ITS DOCUMENTATION, EVEN IF ODIN TELESYSTEMS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. IN NO EVENT WILL ODIN TELESYSTEMS' LIABILITY FOR ANY REASON EXCEED THE ACTUAL PRICE PAID FOR THE PRODUCT AND ITS DOCUMENTATION. SOME JURISDICTIONS DO NOT ALLOW THE LIMITATION OR EXCLUSION OF LIABILITY FOR INCIDENTAL AND CONSEQUENTIAL DAMAGES, SO THE ABOVE LIMITATION OR EXCLUSION MAY NOT APPLY.

Odin TeleSystems Inc. http://www.OdinTS.com

This document is published by:

Odin TeleSystems Inc.

800 East Campbell Road, Suite 334

Richardson, Texas 75081

U. S. A.

# 1. Abstract

This document provides a technical description of Odin TeleSystems' Thor-8-PCIe adapter card. This presentation is targeted to systems integrators and application developers who are developing telecommunications systems and/or software applications using the Thor-8-PCIe platform. The purpose of this document is to provide the needed information about the hardware to allow software developers to efficiently integrate Thor-8-PCIe into their overall system under design.

For information on how to develop host applications utilizing the OTX Hardware Device Driver Application Programming Interface (API), please refer to the "*Programmer's Guide for OTX Hardware API*" document (Odin TeleSystems Inc. document number 1411-1-SAA-1006-1). For help on how to install the Thor-8-PCIe card and the OTX Device Driver Software, please refer to the "*Installation Guide for OTX PCI and PCIe Adapters*" (Odin document number 1512-1-HCA-1001-1).

# 2. Table of Content

| 1. | Abstr                       | act            |                                        | 3  |

|----|-----------------------------|----------------|----------------------------------------|----|

| 2. | Table                       | of Conte       | nt                                     | 4  |

| 3. | Introduction to Thor-8-PCIe |                |                                        | 5  |

| 4. | Speci                       | Specifications |                                        |    |

| 5. | Supp                        | orted Driv     | ver Devices                            | 6  |

|    | 5.1                         | Physic         | al Devices                             | 6  |

|    | 5.2                         | •              | al Devices                             |    |

| 6. | Syste                       | m Archite      | ecture                                 | 8  |

|    | 6.1                         | Extern         | al Interfaces                          | 8  |

|    |                             | 6.1.1          | PCIe Host Bus Interface                | 9  |

|    |                             | 6.1.2          | H.100 Computer Telephony Bus Interface | 10 |

|    |                             | 6.1.3          | Centronics Network Interfaces          |    |

|    |                             | 6.1.4          | OTX ASM Interface                      | 14 |

|    |                             | 6.1.5          | External Clock Connector               | 15 |

|    |                             | 6.1.6          | JTAG Interface                         | 15 |

|    | 6.2                         | Data A         | Architecture                           | 15 |

|    | 6.3                         | Contro         | Control Architecture                   |    |

|    | 6.4                         | Clock          | Architecture                           | 18 |

|    | 6.5                         | Logica         | al Subsystems                          | 20 |

|    |                             | 6.5.1          |                                        |    |

|    |                             |                | 6.5.1.1 Line Configurations            | 20 |

|    |                             |                | 6.5.1.2 Fault Monitoring               | 21 |

|    |                             |                | 6.5.1.3 Loopbacks                      | 22 |

|    |                             | 6.5.2          | Switching Subsystem                    |    |

|    |                             | 6.5.3          | DMA Subsystem                          | 22 |

| 7  | Sunn                        | ort Inforn     | nation                                 | 23 |

# 3. Introduction to Thor-8-PCIe

Thor-8-PCIe is multi-purpose T1/E1 interface adapter. The Thor-8-PCIe card allows Personal Computers (PCs) and other systems with a PCIe bus to be interfaced with T1/E1 links.

Thor-8-PCIe is a member of the Odin Telecom frameworX (OTX+) product family. Thor-8-PCIe is supported by the OTX device driver and by the OTX Hardware Application Programming Interface (API). Equipped with the appropriate OTX software modules, Thor-8-PCIe can be utilized in a variety of T1/E1, Integrated Services Digital Network (ISDN), Frame Relay, and Signaling System #7 (SS#7) applications.

The Thor-8-PCIe supports eight (8) T1 or E1 interfaces at the speeds of 1.544 Mbps and 2.048 Mbps, respectively. Throughout the document the T1/E1 interfaces are referred to as Line Interfaces (LIs). The same board supports both T1 and E1. The operation mode as well as the line terminating impedance of 75 ohms or 100 ohms are software switchable. The card also supports a high-impedance mode with external 20db amplifier for monitoring Consequently, the Thor-8-PCIe card can be used to terminate eight (8) T1/E1 links or to monitor four (4) links.

The Thor-8-PCIe provides H.100 Computer Telephony Bus. The H.100 bus comprises of thirty-two (32) 2, 4, or 8 Mbit/s Time-Division Multiplexed (TDM) highways for board-to-board communication. On the Thor-8-PCIe board the H.100 highways are connected to a non-blocking time-space switch. The time-space switch allows 512 time-slots to be switched between H.100 highways and the local highways. 1024 time-slots can be switched locally between on-board devices. The H.100 bus is backwards compatible with the MVIP bus and the SCBus.

The Thor-8-PCIe board also contains an OTX Application Specific Module (ASM) socket. The ASM interface can be used to add daughter boards providing additional resources. For example, Thor-8-PCIe can be augmented with Vidar-55x4-ASM providing 4 TI TMS320C5510 Digital Signal Processors (DSPs). By loading and running different programs in these DSPs, the Thor-8-PCIe adapter can support a variety of different telecom functions, such as tone detection and generation, HDLC sending and receiving, voice encoding and decoding, etc.

Finally, Thor-8-PCIe contains four (4) codecs. The codecs perform Analog-to-Digital (A/D) and Digital-to-Analog (D/A) conversions. Both the A-law and the u-law are supported. The codecs can be switched to any time-slots on the board. Standard handsets can be connected to the codecs to provide phone functionality.

# 4. Specifications

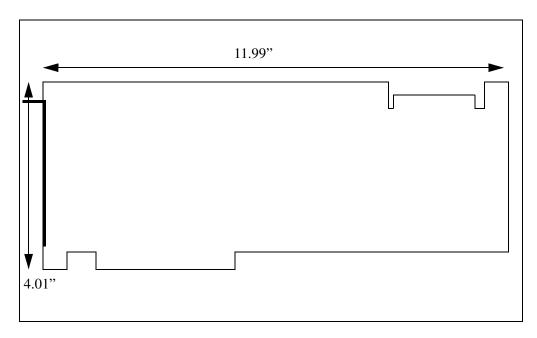

Thor-8-PCIe is a full-length PCIe board. The physical dimensions of Thor-8-PCIe are shown in Figure 1.

Figure 1. Thor-8-PCIe Physical Dimensions (inches).

The Thor-8-PCIe operates with +3.3 supply voltage. It is universally compatible with 3.3 volt of 5 volt signalling.

# 5. Supported Driver Devices

# **5.1 Physical Devices**

The Thor-8-PCIe supports the following physical API driver devices:

Max **Host Device** # **Description Device Type** OTX\_DEVICE\_THOR\_8\_PCI\_PLUS **Board Device** T1/E1 Line Interface OTX\_DEVICE\_THOR\_8\_PCI\_PLUS  $OTX\_DEVICE\_LI\_T1E1$ 8 Devices OTX\_DEVICE\_THOR\_8\_PCI\_PLUS OTX\_DEVICE\_TSS 1 Time-Space Switch OTX\_DEVICE\_THOR\_8\_PCI\_PLUS  $OTX\_DEVICE\_CODEC$ 4 Codec performing A/D and D/A conversions for analog front ends. OTX\_DEVICE\_THOR\_8\_PCI\_PLUS  $OTX\_DEVICE\_VIDAR\_5x\_ASM$ Vidar-5x4-ASM Daughter Board (OPTIONAL)

TABLE 1. OTX Physical Driver Devices supported by Thor-8-PCIe

TABLE 1. OTX Physical Driver Devices supported by Thor-8-PCIe

| Host Device                | Device Type               | Max<br># | Description                                 |

|----------------------------|---------------------------|----------|---------------------------------------------|

| OTX_DEVICE_THOR_8_PCI_PLUS | OTX_DEVICE_VIDAR_55x4_ASM | 1        | Vidar-55x4-ASM Daughter<br>Board (OPTIONAL) |

| OTX_DEVICE_THOR_8_PCI_PLUS | OTX_DEVICE_VIDAR_CST_ASM  | 1        | Vidar-CST-ASM Daughter<br>Board (OPTIONAL)  |

| OTX_DEVICE_THOR_8_PCI_PLUS | OTX_DEVICE_VIDAR_V90_ASM  | 1        | Vidar-V90-ASM Daughter<br>Board (OPTIONAL)  |

# **5.2 Logical Devices**

The Thor-8-PCIe supports the following logical API driver devices:

TABLE 2. OTX Logical Driver Devices supported by Thor-8-PCIe

| Host Device        | Device Type                              | Max<br># | Description                                                        |

|--------------------|------------------------------------------|----------|--------------------------------------------------------------------|

| OTX_DEVICE_LI_T1E1 | OTX_LDEVICE_HDLC_SENDER                  | 1        | Logical Device for sending<br>Hdlc Framing                         |

| OTX_DEVICE_LI_T1E1 | OTX_LDEVICE_HDLC_RECEIVER                | 1        | Logical Device for receiving Hdlc framing.                         |

| OTX_DEVICE_LI_T1E1 | OTX_LDEVICE_CAS_TIEI_SENDE<br>R_RECEIVER | 1        | Logical Device for T1/E1<br>Channel Associated Signalling<br>(CAS) |

In addition, DSPs on an ASM board can be loaded with various program packages to provide support for a variety of Logical Devices types. For example, the Signal Processing Package Two (OtxSpm2) for Vidar-ASM daughter boards provides support for the following API logical devices:

- OTX\_LDEVICE\_HDLC\_SENDER

- OTX\_LDEVICE\_HDLC\_RECEIVER

- OTX\_LDEVICE\_DATA\_RAW\_SENDER

- OTX\_LDEVICE\_DATA\_RAW\_RECEIVER

- OTX\_LDEVICE\_TONE\_FSK\_DETECTOR

- OTX\_LDEVICE\_TONE\_DTMF\_DETECTOR

- OTX\_LDEVICE\_TONE\_MF\_DETECTOR

- OTX\_LDEVICE\_TONE\_DUAL\_DETECTOR

- OTX\_LDEVICE\_TONE\_SINGLE\_DETECTOR

- OTX\_LDEVICE\_TONE\_DTMF\_GENERATOR

- OTX\_LDEVICE\_TONE\_DTMF\_DIALER

- OTX\_LDEVICE\_TONE\_MF\_DIALER

- OTX\_LDEVICE\_TONE\_EFFECTS\_GENERATOR

- OTX\_LDEVICE\_DATA\_CONVERTER

- OTX\_LDEVICE\_TONE\_CONST\_VAL\_GENERATOR

- OTX\_LDEVICE\_TONE\_VAL\_SAMPLER

- OTX\_LDEVICE\_TONE\_SINEWAVE\_GENERATOR

- OTX\_LDEVICE\_TONE\_SILENCE\_DETECTOR

For mode information on the physical and logical driver devices, please refer to "*Programmer's Guide for OTX Hardware API*" (Odin document # 1412-1-SAA-1006-1).

# 6. System Architecture

The overall system architecture can be best described and understood through different architectural views or aspects. This document explores the systems architecture from the following angles:

- 1. **External Interface View:** The external interface view describes the external interfaces of the adapter board, and how they are connected to the various internal devices and modules.

- 2. **Data Architecture View:** The data architecture view illustrates how the Time Division Multiplexed (TDM) serial data is connected and transferred through the board.

- 3. **Control Architecture View:** The control architecture view describes how the internal devices and modules can be controlled by the host processor.

- 4. **Clock Architecture View:** The clock architecture view specifies what clocking and synchronization options are available, how clocking is derived, and how it distributed to the various devices.

- 5. **Logical Subsystem View:** The logical subsystem view describes the logical design subsystems in the system. Each subsystem can comprise hardware, firmware and driver or on-board processor software.

It is important to note that one device within the board can be involved in several of these views, each view describing how one aspect of the device interfaces with other devices.

#### **6.1 External Interfaces**

The Thor-8-PCIe contains the following external interfaces:

- PCIe Host Bus

- H.100 Computer Telephony Bus

- Centronics Network Interface with

- 8 T1/E1 Line Interfaces

- 4 Analog Interfaces for Handsets

- OTX ASM Socket

- JTAG Port for DSP Control

- 1 External Synchronization Clock Input

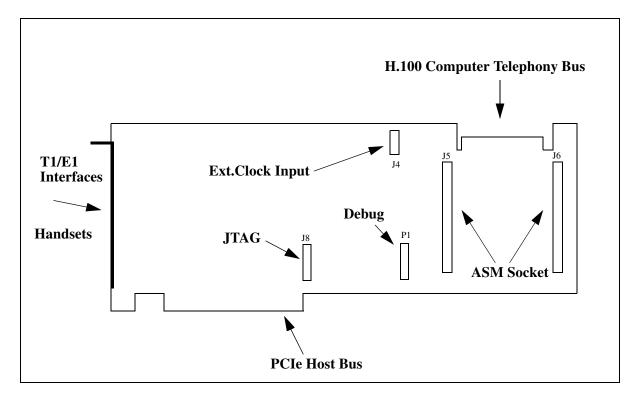

The external interfaces of the Thor-8-PCIe card are illustrated in Figure 2.

Figure 2. Thor-8-PCIe External Interfaces.

# 6.1.1 PCIe Host Bus Interface

The interface between the Thor-8-PCIe board and the Host Computer is the PCIe r1.0a (single lane). A single lane card like Thor-8-PCIe can also be plugged into mult-lane PCIe slots.

# 6.1.2 H.100 Computer Telephony Bus Interface

Thor-8-PCIe supports the H.100 Computer Telephony Bus standard. The H.100 bus is a collection of time-division multiplexed (TDM) digital telephony highways designed to carry telephony traffic between extensions boards within one PC chassis. The H.100 bus supports 32 TDM highways. The highways can be operated at 2.048, 4.096, or 8.192 MBit/s carrying 32, 64, or 128 64 kbit/s time-slots, respectively. Up to 20 boards can be connected to one H.100 bus. The maximum distance between boards is 7 inches.

Within the PC chassis the data streams are passed from card to card using a 60 pin ribbon cable and AMP 1-557089-2 connectors. The H.100 connector is a 60-finger edge connector on the upper right-hand side (Figure 2) of the board. The pin-out of the H.100 connector is listed in Table 3.

TABLE 3. Thor-8-PCIe H.100 Pin Assignments

| Pin | Signal                                         | Pin | Signal                             |

|-----|------------------------------------------------|-----|------------------------------------|

| 1   | Reserved                                       | 2   | Power to active devices (CT_+5Vdc) |

| 3   | TDM Highway 31 (CT_D31)                        | 4   | TDM Highway 30 (CT_D30)            |

| 5   | TDM Highway 29 (CT_D29)                        | 6   | TDM Highway 28 (CT_D28)            |

| 7   | GND                                            | 8   | TDM Highway 27 (CT_D27)            |

| 9   | TDM Highway 26 (CT_D26)                        | 10  | TDM Highway 25 (CT_D25)            |

| 11  | TDM Highway 24 (CT_D24)                        | 12  | GND                                |

| 13  | TDM Highway 23 (CT_D23)                        | 14  | TDM Highway 22 (CT_D22)            |

| 15  | TDM Highway 21 (CT_D21)                        | 16  | TDM Highway 20 (CT_D20)            |

| 17  | GND                                            | 18  | TDM Highway 19 (CT_D19)            |

| 19  | TDM Highway 18 (CT_D18)                        | 20  | TDM Highway 17 (CT_D17)            |

| 21  | TDM Highway 16 (CT_D16)                        | 22  | GND                                |

| 23  | TDM Highway 15 (CT_D15)                        | 24  | TDM Highway 14 (CT_D14)            |

| 25  | TDM Highway 13 (CT_D13)                        | 26  | TDM Highway 12 (CT_D12)            |

| 27  | GND                                            | 28  | TDM Highway 11 (CT_D11)            |

| 29  | TDM Highway 10 (CT_D10)                        | 30  | TDM Highway 9 (CT_D9)              |

| 31  | TDM Highway 8 (CT_D8)                          | 32  | GND                                |

| 33  | TDM Highway 7 (CT_D7)                          | 34  | TDM Highway 6 (CT_D6)              |

| 35  | TDM Highway 5 (CT_D5)                          | 36  | TDM Highway 4 (CT_D4)              |

| 37  | GND                                            | 38  | TDM Highway 3 (CT_D3)              |

| 39  | TDM Highway 2 (CT_D2)                          | 40  | TDM Highway 1 (CT_D1)              |

| 41  | TDM Highway 0 (CT_D0)                          | 42  | GND                                |

| 43  | Frame Sync from "A" Clock Master (/CT_FRAME_A) | 44  | GND                                |

TABLE 3. Thor-8-PCIe H.100 Pin Assignments

| Pin | Signal                                                      | Pin | Signal                    |

|-----|-------------------------------------------------------------|-----|---------------------------|

| 45  | Bit Clock from "A" Clock Master (CT_C8_A)                   | 46  | GND                       |

| 47  | Secondary Network Timing Reference (CT_NETREF)              | 48  | GND                       |

| 49  | Redundant Frame Sync from "B" Clock<br>Master (/CT_FRAME_B) | 50  | GND                       |

| 51  | Redundant Bit Clock from "B" Clock Master (CT_C8_B)         | 52  | GND                       |

| 53  | Message Channel (CT_MC)                                     | 54  | GND                       |

| 55  | Compatibility Frame Pulse (/FR_COMP)                        | 56  | GND                       |

| 57  | SCbus System Clock (SCLK)                                   | 58  | GND                       |

| 59  | SCbus System Clock time two (SCLKx2)                        | 60  | GND                       |

| 61  | MVIP-90 bit clock (C2)                                      | 62  | GND                       |

| 63  | MVIP-90 bit clock time two (/C4)                            | 64  | GND                       |

| 65  | H-MVIP 16 Mhz Clock (/C16+)                                 | 66  | H-MVIP 16 Mhz Clock /C16- |

| 67  | GND                                                         | 68  | RESERVED                  |

For more information on the H.100 bus, please contact the Enterprise Computer Telephony Forum, ECTF, *http://www.ectf.org* .

## **6.1.3** Centronics Network Interfaces

The back panel of Thor-8-PCIe contains a Centronics connector with 50 contacts. The Centronics connector provides the following interfaces:

- 8 T1/E1 4-wire Line Interfaces

- 4 Analog Interfaces for Handsets

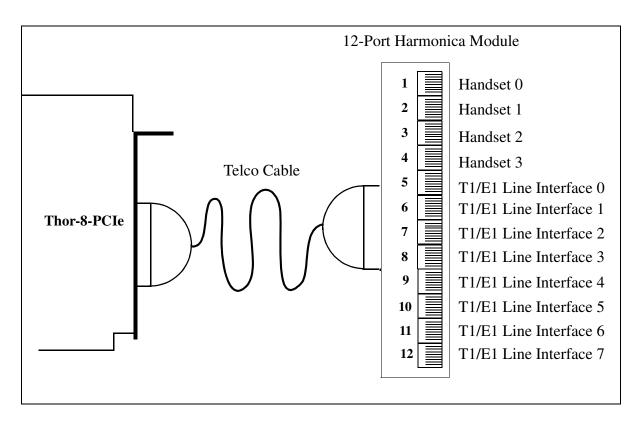

Thor-8-PCIe is delivered with a telco-type connector cable (SCSI Cable) and a Harmonica module which converts from Centronics connector to 12 RJ-11 connectors. The Harmonica module allows the connection of T1/E1 lines and handsets to Thor-8-PCIe using RJ-45 and RJ-11 connectors (See Figure 3).

Figure 3. Thor-8-PCIe Harmonica Module

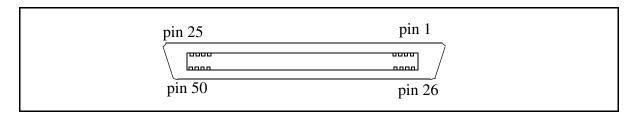

Although Thor-8-PCIe is delivered with the RJ-45 and RJ-11 Harmonica module, the modular structure of Thor-8-PCIe allows it to be adapted for other types of connectors as well. For example, if the application requires BNC or Bantam type connectors, the Harmonica module can be replaced with another type of adapter which converts from Centronics to BNC or Bantam type connectors. The pin-outs of the Centronics and the RJ connectors are documented in Figure 4 and in Table 4.

Also available as optional accessories are 19" rack-mountable harmonicas (BNC and RJ-45 versions).

Figure 4. Thor-8-PCIe Centronics Connector.

TABLE 4. Thor-8-PCIe Centronics Connector Pin Assignments

| Pin | Signal                                | Pin | Signal                                 |

|-----|---------------------------------------|-----|----------------------------------------|

| 1   | Codec-0, Speaker (+)                  | 26  | Codec-0, Speaker (-)                   |

| 2   | Codec-0, Handset Microphone (+)       | 27  | Codec-0, Handset Microphone Ground     |

| 3   | Codec-1, Speaker (+)                  | 28  | Codec-1, Speaker (-)                   |

| 4   | Codec-1, Handset Microphone (+)       | 29  | Codec-1, Handset Microphone Ground     |

| 5   | Codec-2, Speaker (+)                  | 30  | Codec-2, Speaker (-)                   |

| 6   | Codec-2, Handset Microphone (+)       | 31  | Codec-2, Handset Microphone Ground     |

| 7   | Codec-3, Speaker (+)                  | 32  | Codec-3, Speaker (-)                   |

| 8   | Codec-3, Handset Microphone (+)       | 33  | Codec-3, Handset Microphone Ground     |

| 9   |                                       | 34  |                                        |

| 10  | Line Interface 0, Transmit Line (tip) | 35  | Line Interface 1, Transmit Line (ring) |

| 11  | Line Interface 0, Receive Line (tip)  | 36  | Line Interface 1, Receive Line (ring)  |

| 12  | Line Interface 1, Transmit Line (tip) | 37  | Line Interface 1, Transmit Line (ring) |

| 13  | Line Interface 1, Receive Line (tip)  | 38  | Line Interface 1, Receive Line (ring)  |

| 14  | Line Interface 2, Transmit Line (tip) | 39  | Line Interface 2, Transmit Line (ring) |

| 15  | Line Interface 2, Receive Line (tip)  | 40  | Line Interface 2, Receive Line (ring)  |

| 16  | Line Interface 3, Transmit Line (tip) | 41  | Line Interface 3, Transmit Line (ring) |

| 17  | Line Interface 3, Receive Line (tip)  | 42  | Line Interface 3, Receive Line (ring)  |

| 18  | Line Interface 4, Transmit Line (tip) | 43  | Line Interface 4, Transmit Line (ring) |

| 19  | Line Interface 4, Receive Line (tip)  | 44  | Line Interface 4, Receive Line (ring)  |

| 20  | Line Interface 5, Transmit Line (tip) | 45  | Line Interface 5, Transmit Line (ring) |

| 21  | Line Interface 5, Receive Line (tip)  | 46  | Line Interface 5, Receive Line (ring)  |

| 22  | Line Interface 6, Transmit Line (tip) | 47  | Line Interface 6, Transmit Line (ring) |

| 23  | Line Interface 6, Receive Line (tip)  | 48  | Line Interface 6, Receive Line (ring)  |

| 24  | Line Interface 7, Transmit Line (tip) | 49  | Line Interface 7, Transmit Line (ring) |

| 25  | Line Interface 7, Receive Line (tip)  | 50  | Line Interface 7, Receive Line (ring)  |

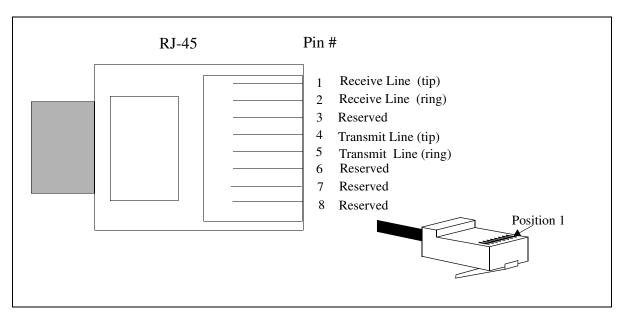

The RJ-45 pin-outs in the Harmonica module for the 4-wire T1/E1 line interfaces are shown in Figure 5.

Figure 5. RJ-45 Connector for the T1 or E1 Interface.

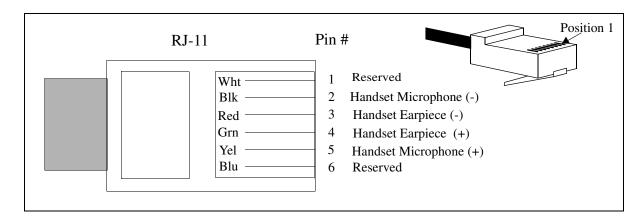

The RJ-11 pin out for the handsets is shown in Figure 6.

Figure 6. RJ-11 Connector for the Handsets.

#### **6.1.4 OTX ASM Interface**

The Thor-8-PCIe board contains an OTX ASM (Application Specific Module) Interface (Reference Designators J5 and J6). The ASM Interface can be used to attach a daughter board modules to the Thor-8-PCIe board. The ASM daughter boards can add functionality, such as DSP or HDLC resources.

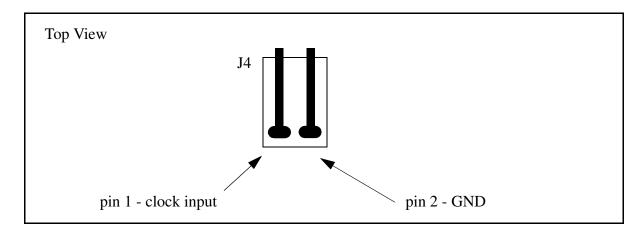

#### 6.1.5 External Clock Connector

The Thor-8-PCIe board can be clocked by supplying a external 8kHz clock signal to the J4 connector. The clock signal can be a 3.3V or 5V signal. The location of the J4 connector is show in Figure 2. The pinout of the J4 connector is shown in Figure 7.

Figure 7. External Clock Connector.

## 6.1.6 JTAG Interface

The JTAG port (reference designator J3) are used for:

- · Board Testing

- Programming of Complex Programmable Logical Devices (CPLDs)

- Connecting the DSP emulator board for DSP Software Development.

For more information on how to use the JTAG port and the DSP emulator, please refer to "*Programmer's Guide for OTX C55x DSP Software Development Kit*" Odin Document # 1412-1-SAA-1007-1.

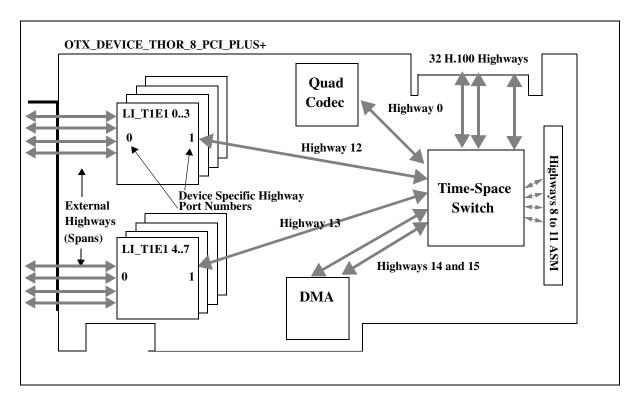

#### **6.2** Data Architecture

Internally, Thor-8-PCIe utilizes serial TDM (Time-Division Multiplexed) data streams for transfer of data or voice. The internal serial TDM data streams are called "Highways." External interfaces are called spans.

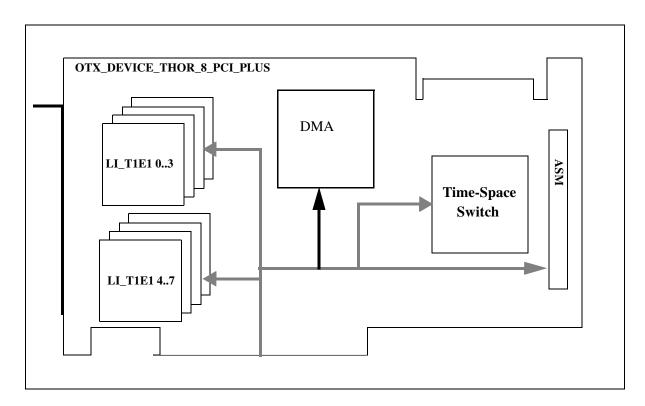

The serial highways provide data paths between physical devices as shown in Figure 8. If the physical device connects to more than one highway, the device specific highway port number is also shown in Figure 8.

Figure 8. Thor-8-PCIe Highway Connections.

The Thor-8-PCIe internal highways are configured to operate at ether 2, 4, or 8 Mbit/s, each containing 32, 64 or 128 8-bit time-slots, respectively. The data rate of one time-slot is 64 kbit/s. Table 5 lists the internal highways used on Thor-8-PCIe boards.

**TABLE 5. Thor-8-PCIe Highway Connections**

| Highway # | Connecting Time-Space Switch to                                            |

|-----------|----------------------------------------------------------------------------|

| 0         | 2.048 Mbits/s Highway connecting to Codec#0, Codec#1, Codec#2, and Codec#3 |

| 8-11      | 4.096 Mbits/s Highway connecting to ASM connectors                         |

| 12-13     | 8.192 Mbits/s Highway connecting to the LIUs                               |

| 14-15     | 8.192 Mbits/s Highway connecting to the DMA system                         |

The time-space switch in non-blocking and allows any internal time-slot on any internal highway to be switched to any other highway/time-slot. The cross-connections are software programmable and automatically taken care of by the OTX driver.

In addition, the Thor-8-PCIe contains 32 H.100 Highways:

The Thor-8-PCIe time-space also provides support multicasting and messaging. In

multicasting mode any input channel can be cross-connected to multiple output channels. For example, an incoming Li time slot can be both switched to an outgoing H.100 Highway and it can also be switched to the ASM board.

In the messaging mode, the time-space switch can be instructed to send a constant byte on any time slot. Once activated, every byte on the specified time slot will contain the same value. The generation of constant byte does not consume any processing capacity. The constant byte feature is useful in, for example, verification of a through connection or in Bit Error Rate (BER) testing.

# **6.3 Control Architecture**

The host PC can control the physical devices on the Thor-8-PCIe board through the PCIe bus. The Thor-8-PCIe control architecture is illustrated in Figure 9.

Figure 9. Thor-8-PCIe Control Architecture.

#### **6.4 Clock Architecture**

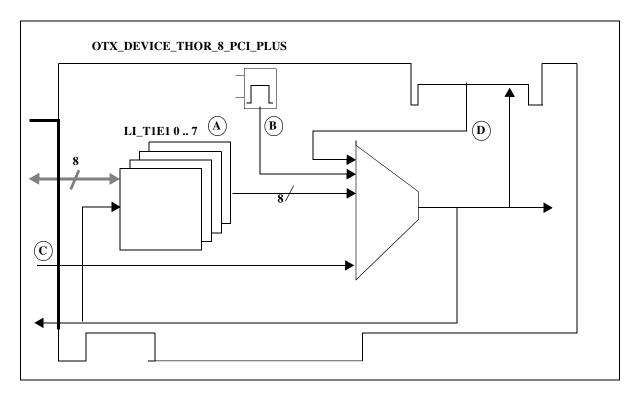

On the Thor-8-PCIe board all the internal TDM data highways and the all the devices processing TDM data are synchronized to one clock reference. The clock reference can be derived from multiple sources and then switched to all the devices. The clocking sources supported by Thor-8-PCIe are illustrated in Figure 10 and listed in Table 6.

Figure 10. Thor-8-PCIe Clock Architecture Overview.

TABLE 6. Thor-8-PCIe Clocking Sources.

| Clock<br>Source | Description                                                                                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| A               | 8 kHz frame clock extracted from one of the incoming T1/E1 spans (0-7). OTX_CLOCK_SOURCE_LOCAL_0 through OTX_CLOCK_SOURCE_LOCAL_7              |

| В               | On-board free running oscillator. OTX_CLOCK_SOURCE_INTERNAL                                                                                    |

| С               | External 8 kHz framing clock. OTX_CLOCK_SOURCE_EXTERNAL                                                                                        |

| D               | H.100 Reference Clock. OTX_CLOCK_SOURCE_A_CLOCKS, OTX_CLOCK_SOURCE_A_CLOCKS_ETCF, OTX_CLOCK_SOURCE_B_CLOCKS, or OTX_CLOCK_SOURCE_B_CLOCKS_ETCF |

In the event that the clocking source is lost, Thor-8-PCIe will automatically switch to a backup clocking source. For example, if clocking is derived from an incoming T1/E1 span, and the span experiences Loss of Signal (LOS), the clocking source is automatically switched to the other T1/E1 span. If the other span loses signal as well, then

Thor-8-PCIe will switch to free-running mode and the clocking will be derived from the on-board oscillator. If the H.100 clocks or the external clocks are used as the clocking source and the clocking is lost, Thor-8-PCIe will switch into free-running mode and use the on-board oscillator.

It is important to understand that the difference between the clocks on the external T1/E1 spans and the internal clocks. When the Thor-8-PCIe clocking is derived from one incoming T1/E1 span, the external T1/E1 span and the internal highways on-board are completely synchronized. In that case, the other T1/E1 span is not necessarily in synchronization with the internal highways. To compensate for that, Thor-8-PCIe implements an elastic receive buffer with a size of 64x8 bits. The elastic store is used to adapt the clock rates between the T1/E1 clock and the Thor-8-PCIe system clock, to compensate for input wonder and jitter, and to align the received frame with the internal highway frame. However, the elastic buffer may eventually over- or underflow and a slip condition may occur. When a positive or negative slip occurs, Thor-8-PCIe will discard one received layer-1 frame to free space in the elastic receive buffer and to continue forwarding the data from incoming T1/E1 span to the internal highway. The slip condition will cause a one 8-bit data sample to be discarded on all of the time-slots.

The occurrence of slips is normal in telephone network. A loss of data sample in a voice data is insignificant cannot be detected by human ear. Loss of one data byte in a data transmission is typically detected with Cyclic Redundancy Checks (CRC). A loss of a data byte due to a slip is typically corrected by the data link protocol requesting a retransmission of the corrupted packet.

## **6.5** Logical Subsystems

The logical subsystem view describes the logical design subsystems within the Thor-8-PCIe adapter. Each subsystem can comprise hardware, firmware, and driver or on-board processor software. The Thor-8-PCIe consists of two subsystems:

- 1. Line Interface Subsystem

- 2. Switching Subsystem

- 3. DMA Subsystem

#### **6.5.1** Line Interface Subsystem

The Line Interface subsystem is responsible for interfacing the Thor-8-PCIe card with the external T1/E1 links. The subsystem provides the connectors, terminating resistors, transformers, and overvoltage protection.

#### **6.5.1.1** Line Configurations

The Thor-8-PCIe line interfaces support several different line codes:

• HDB3 - High Density Bipolar 3

- B8ZS Bipolar 8 Zero Substitution

- AMI Alternate Mark Inversion

- AMI with NZC

For the T1 operation mode, the following framing formats can be used:

- F4 4-frame multiframe

- F12 12 frame multiframe

- ESF Extended Superframe

- F72 72 frame multiframe

For the E1 operation mode, Thor-8-PCIe supports the following framing formats:

- Doubleframe

- · CRC multiframe

## **6.5.1.2 Fault Monitoring**

The line interface subsystem supports fault and performance monitoring. The transceiver subsystem detects and reports the following alarms in the receive streams:

- Framing errors

- Cyclic Redundancy Check (CRC) errors

- Code violations

- Loss of frame alignment

- Loss of Signal (LOS)

- Alarm Indication Signal (AIS)

- E bit errors (E1 only)

- Slip

- Remote Alarm Indication (RAI, Yellow Alarm)

The line interface subsystems also supports the transmitting of the following alarms towards the remote end:

- Alarm Indication Signal (AIS)

- Remote Alarm Indication (RAI, Yellow alarm)

- Auxiliary Pattern (AUXP)

## 6.5.1.3 Loopbacks

The line interface subsystem implements a remote loopback for line testing. In the remote loopback mode, the clock and data recovered from the line inputs are routed back to the line outputs through the analog transmitter.

## **6.5.2** Switching Subsystem

The switching subsystem provides a time-space switch for the switching of any incoming time/slot to any outgoing time slot. This subsystem is also responsible for delivering and switching of the on-board clock signals. The switching subsystem has already been covered in Chapter 6.2: "Data Architecture" and Chapter 6.4: "Clock Architecture".

# 6.5.3 DMA Subsystem

The Thor-8-PCIe board contains a Direct Memory Access (DMA) system allowing the user to send two 8 MHz highways of data directly into and from the host PC's memory. This greatly reduces the host CPU time required for data transfer to or from the host. The time-space switch can be used to cross-connect the DMA system into any incoming or outgoing time-slot in the Line Interface, ASM, or H.100 Highways.

# 7. Support Information

For more information on this product, please contact:

Odin TeleSystems Inc. 800 East Campbell Road, Suite 334 Richardson, Texas 75081 U. S. A.

Tel: +1-972-664-0100 Fax: +1-972-664-0855 Email: Info@OdinTS.com URL: http://www.OdinTS.com